# **Description**

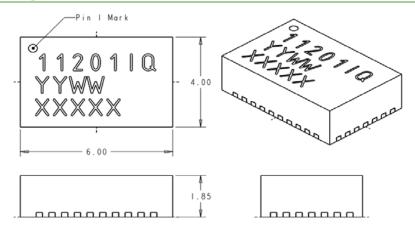

The SD11201IQ Power Module is a high efficiency, synchronous step-down (Buck) DC-DC converter capable of delivering 1A continuous current. The SD11201IQ is assembled in an advanced 6mm x 4mm x 1.85mm 34-pin QFN package, that integrates an inductor, MOSFET switches, small-signal circuits, and compensation.

The SD11201IQ Power Module operates over an input voltage range up to 16V and applies a Constant-on-time (COT) control scheme which provides very fast load transient response and easy loop design. It integrates full protection features, including short-circuit protection, over-current protection, under voltage protection, and thermal shutdown to make the part operate safely.

The SD11201IQ Power Module requires a minimal number of readily available, standard, external components which significantly helps in system design and productivity by offering greatly simplified board design, layout, and manufacturing requirements. In addition, a reduction in the number of components required for the complete power solution helps to enable an overall system cost saving. The SD11201IQ Power Module is RoHS compliant and lead-free manufacturing environment compatible.

### **Module Form Factor**

**6x4 QFN Package**

# **Applications**

- Point of Load Conversion for 7V 16V input rail

- Space constrained and noise sensitive applications

- High Thermal requirement applications

- Storage (SSD, HDD), Embedded, LV I/O System Power

- FPGAs, ASICs, DSPs, Network processors, Industrial applications

- Security Cameras, Test and Measurement, Portable devices, Medical devices

### **Features**

- Excellent Ripple (<2mV) and Transient Performance

- Up to 1A Continuous Operating Current

- Up to 16V Input Voltage Range

- 1.5% Vfb Initial Accuracy

- 890kHz Switching Frequency

- Optimized Solution Size

- Thermal, Over-Current, Short Circuit, Under-Voltage and Pre-Bias Protections

- 455μA Low Quiescent Current

- RoHS Compliant, MSL Level 3, 260°C Reflow

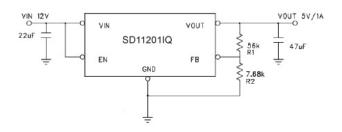

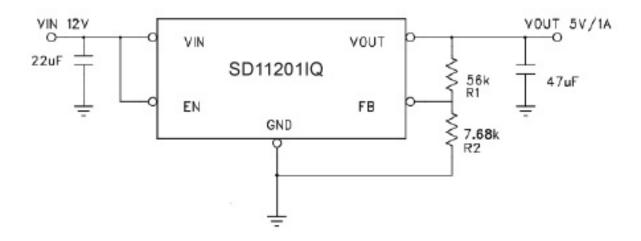

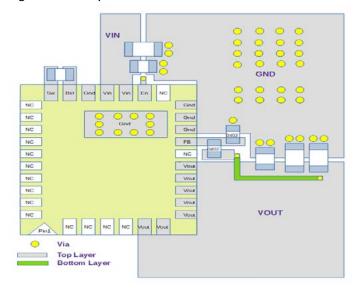

**Figure 1: Simplified Applications Circuit**

# **SD11201IQ Power Module**

# **Ordering Information**

| Part Number   | Package Marking | T <sub>A</sub> Rating Package Description                   |  |  |  |

|---------------|-----------------|-------------------------------------------------------------|--|--|--|

| SD11201IQ     | 11201IQ         | -40°C ≤ T <sub>A</sub> ≤ 85°C 6mm x 4mm x 1.85mm 34-pin QFN |  |  |  |

| SD11201IQ-EVB | 11201IQ         | Customer Evaluation Board                                   |  |  |  |

## **Pin Functions**

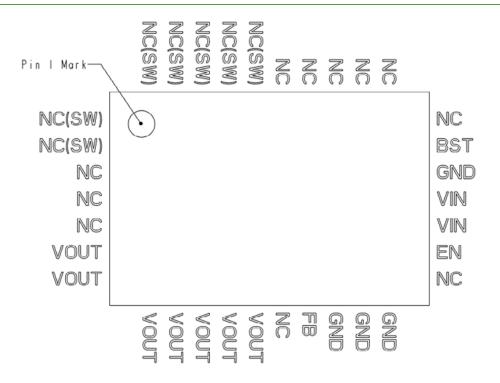

Figure 2: Pin Diagram (Top View)

**NOTE A**: NC pins are not to be electrically connected to each other or to any external signal, ground or voltage. However, they must be soldered to the PCB. Failure to follow this guideline may result in part malfunction or damage.

**NOTE B**: White 'dot' on top left is pin 1 indicator on top of the device package.

# **Pin Descriptions**

| PIN                                                                                                                                                        | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 30, 31, 32, 33, 34                                                                                                                                   | NC(SW) | No Connect. These pins are internally connected to the common switching node of the internal MOSFETs. They must be soldered to PCB but not be electrically connected to any external signal, ground, or voltage. Failure to follow this guideline may result in device damage.                                  |

| 3, 4, 5,13,18,24,25<br>26,27,28,29                                                                                                                         | NC     | No Connect. These pins must be soldered to PCB but not electrically connected to each other or to any external signal, voltage, or ground. These pins may be connected internally. Failure to follow this guideline may result in device damage.                                                                |

| Regulated converter output. Connect to the load and place output capacitor(s) between these pins and GND pins. Refer to the Layout Recommendation section. |        |                                                                                                                                                                                                                                                                                                                 |

| 15,16,17,22                                                                                                                                                | GND    | Input/Output power ground. Connect to the ground electrode of the input and output filter capacitors. See VOUT and VIN pin descriptions for more details.                                                                                                                                                       |

| 1 20 21 VIN 1 V V V V V V V V V V V V V V V V V V                                                                                                          |        | Input power supply. Connect to input power supply. Decouple with input capacitor to GND pin. Refer to the Layout Recommendation section.                                                                                                                                                                        |

|                                                                                                                                                            |        | Enable pin. Applying logic high to the EN pin will enable the device and initiate a soft-start. Applying logic low disables the output and switching stops. EN can be connected to VIN directly or through a resistor.                                                                                          |

|                                                                                                                                                            |        | External feedback input pin. Connect resistor between FB and GND, and another resistor between FB to VOUT to set the output voltage. Refer to Output Voltage Setting in page 15 for a description of resistor selection.                                                                                        |

| 23 NC(BST)                                                                                                                                                 |        | Bootstrap pin. This pin is internally connected to a capacitor to SW to form a floating supply across the high-side switch driver. This pin must be soldered to PCB but not be electrically connected to any external signal, ground, or voltage. Failure to follow this guideline may result in device damage. |

# **SD11201IQ Power Module**

High Input Voltage, 1A Buck Converter with Integrated Inductor - 4

**CAUTION**: Absolute Maximum ratings are stress ratings only. Functional operation beyond the recommended operating conditions is not implied. Stress beyond the absolute maximum ratings may impair device life. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

**Absolute Maximum Pin Ratings**

|               | 8                 |      |                      |       |

|---------------|-------------------|------|----------------------|-------|

| PARAMETER     | SYMBOL            | MIN  | MAX                  | UNITS |

| Input Voltage | VIN               | -0.3 | 18.0                 | V     |

| Device Enable | EN                | -0.3 | V <sub>IN</sub> +0.3 | V     |

| Feedback      | FB                | -0.3 | 5.5                  | V     |

| Switch Node   | NC(SW) Voltage DC |      | 18.0                 | V     |

| BOOST         | NC(BST)           | -0.3 | 18.0                 | V     |

**Absolute Maximum Thermal Ratings**

| PARAMETER                              | CONDITION                      | MIN | MAX  | UNITS |

|----------------------------------------|--------------------------------|-----|------|-------|

| Maximum Operating Junction Temperature |                                |     | +150 | °C    |

| Storage Temperature Range              |                                | -65 | +150 | °C    |

| Reflow Peak Body Temperature           | (10 Sec) MSL3 JEDEC J-STD-020A |     | +260 | °C    |

**Absolute Minimum ESD Ratings**

| PARAMETER                  | CONDITION | MIN   | MAX | UNITS |

|----------------------------|-----------|-------|-----|-------|

| HBM (Human Body Model)     |           | ±2000 |     | V     |

| CDM (Charged Device Model) |           | ±500  |     | V     |

# **Recommended Operating Conditions**

| PARAMETER                      | SYMBOL           | MIN | MAX  | UNITS |

|--------------------------------|------------------|-----|------|-------|

| Input Voltage Range            | V <sub>IN</sub>  | 7   | 16   | V     |

| Output Voltage Range           | V <sub>OUT</sub> | 0.6 | 5.0  | V     |

| Output Current Range           | I <sub>оит</sub> |     | 1    | А     |

| Operating Junction Temperature | T <sub>J</sub>   | -40 | +125 | °C    |

## **Thermal Characteristics**

| PARAMETER                                           | SYMBOL             | TYPICAL | UNITS |

|-----------------------------------------------------|--------------------|---------|-------|

| Thermal Shutdown                                    | T <sub>SD</sub>    | 150     | °C    |

| Thermal Shutdown Hysteresis                         | T <sub>SDHYS</sub> | 20      | °C    |

| Thermal Resistance: Junction to Ambient (0 LFM) (1) | $\theta_{JA}$      | 19      | °C/W  |

| Thermal Resistance: Junction to Case (0 LFM)        | $\theta_{JC}$      | 1       | °C/W  |

<sup>(1)</sup> Based on 2oz. external copper layers and proper thermal design in line with EIJ/JEDEC JESD51-7 standard for high thermal conductivity boards.

NOTE: V<sub>IN</sub> = 12V, Minimum and Maximum values are over operating ambient temperature, vin, and load range unless otherwise noted. Typical values are at  $T_A = T_J = 25$ °C.

| PARAMETER                                            | SYMBOL               | TEST CONDITIONS                                                      | MIN   | TYP   | MAX   | UNITS |  |

|------------------------------------------------------|----------------------|----------------------------------------------------------------------|-------|-------|-------|-------|--|

| Operating Input Voltage (1)                          | V <sub>IN</sub>      |                                                                      | 7     |       | 16    | V     |  |

| Under Voltage Lock-Out –<br>V <sub>IN</sub> Rising   | V <sub>UVLOR</sub>   | Voltage above which UVLO is not asserted                             | 4.1   | 4.13  | 4.22  | V     |  |

| Under Voltage Lock-Out –<br>V <sub>IN</sub> Falling  | V <sub>UVLOF</sub>   | Voltage below which UVLO is asserted                                 | 3.8   | 3.93  | 4.05  | V     |  |

| Under Voltage Lock-Out<br>Hysteresis                 | V <sub>UVLOHYS</sub> |                                                                      |       | 200   |       | mV    |  |

| Shut-Down Supply Current                             | Is                   | EN = 0V                                                              |       |       | 10    | μΑ    |  |

| No Load Quiescent Current                            | I <sub>VINQ</sub>    | V <sub>OUT</sub> = 1.2V                                              | 210   | 455   | 895   | μΑ    |  |

| Feedback Pin Voltage (2)                             | $V_{FB}$             | V <sub>OUT</sub> = 0.6V, I <sub>LOAD</sub> = 0, T <sub>A</sub> =25°C | 0.596 | 0.605 | 0.614 | V     |  |

| Feedback Pin Voltage (Line,                          | .,                   | $7V \leqslant V_{IN} \leqslant 16V$                                  | 0.595 | 0.605 | 0.615 | .,    |  |

| Load, Temp.)                                         | $V_{FB}$             | $0A \le I_{LOAD} \le 1A$ ; $-40^{\circ}C \le T_A \le 85^{\circ}C$    |       |       |       | V     |  |

| Feedback pin Input Leakage<br>Current <sup>(3)</sup> | I <sub>FB</sub>      | VFB pin input leakage current                                        |       | 18    | 60    | nA    |  |

| V <sub>OUT</sub> Rise Time <sup>(3)</sup>            | t <sub>RISE</sub>    |                                                                      |       | 0.8   | 1.5   | ms    |  |

| Continuous Output Current                            | I <sub>OUT</sub>     |                                                                      | 0     |       | 1     | Α     |  |

| Valley Current Limit Trip<br>Level                   | I <sub>OCP</sub>     | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.2V                       | 4.2   | 4.5   |       | А     |  |

| Current Limit Retry Time (3)                         | T <sub>CL_TRY</sub>  |                                                                      |       | 2.5   |       | ms    |  |

| Disable Threshold                                    | V <sub>DISABLE</sub> | EN pin logic going low                                               |       | 1.05  |       | V     |  |

| Enable Threshold                                     | $V_{EN}$             | EN pin logic going high                                              | 1.1   | 1.2   | 1.4   | V     |  |

| EN Hysteresis                                        | EN <sub>HYS</sub>    |                                                                      |       | 150   |       | mV    |  |

| EN Pin Input Current                                 | I <sub>EN</sub>      | EN = 2.0V                                                            |       | 1.5   | 2     | μΑ    |  |

| Switching Frequency                                  | F <sub>SW</sub>      | Free running frequency of oscillator                                 |       | 890   |       | kHz   |  |

- (1) Minimum Vin voltage must be at least 1.3V higher than Vout.

- (2) The FB pin is a sensitive node. Do not touch FB while the device is in regulation.

- (3) Parameter not production tested but is guaranteed by design.

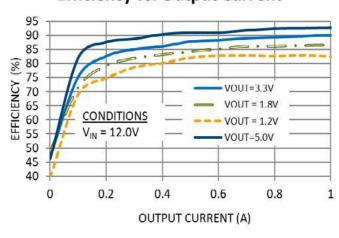

### **Efficiency vs. Output Current**

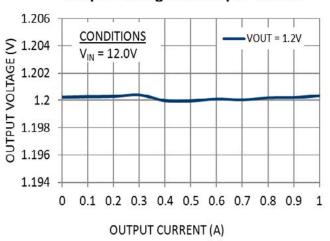

### **Output Voltage vs. Output Current**

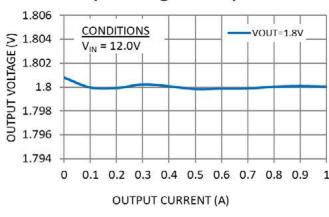

### **Output Voltage vs. Output Current**

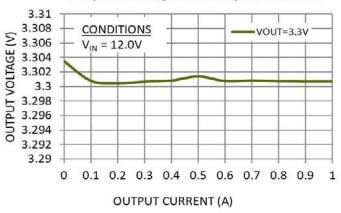

### **Output Voltage vs. Output Current**

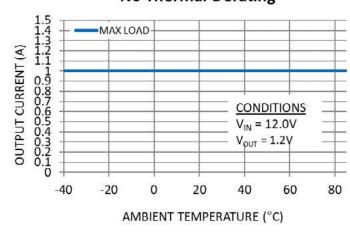

### No Thermal Derating

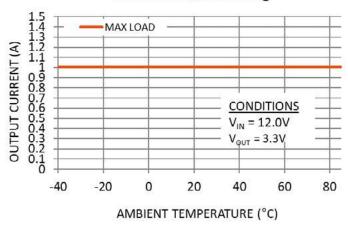

### No Thermal Derating

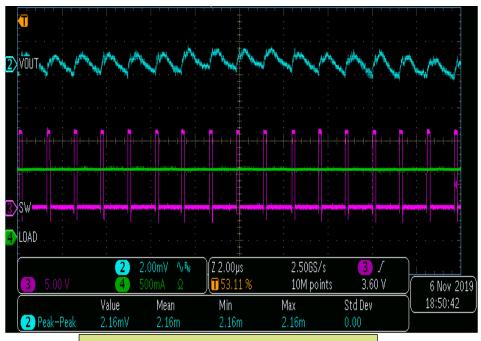

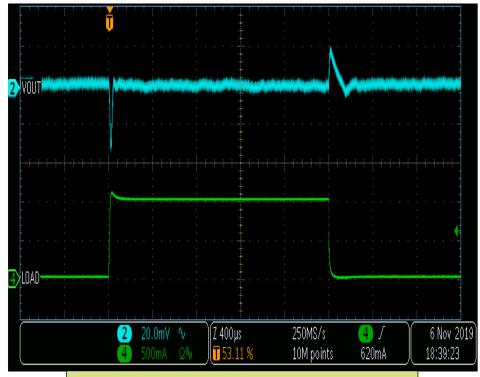

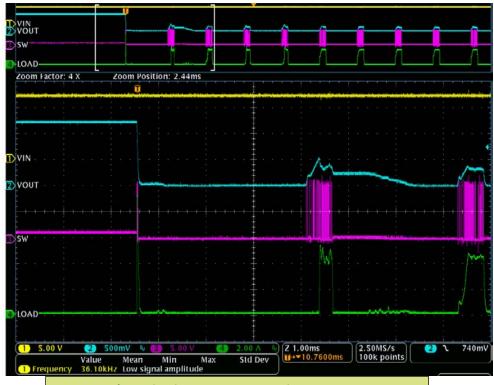

# **Typical Performance Characteristics**

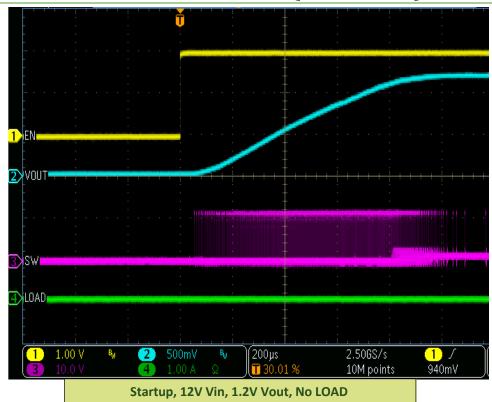

**OUTPUT Ripple, 12V Vin, 1.2V Vout, 1A DC**

Load Transient Response, 12V Vin, 1.2V Vout, 1A DC

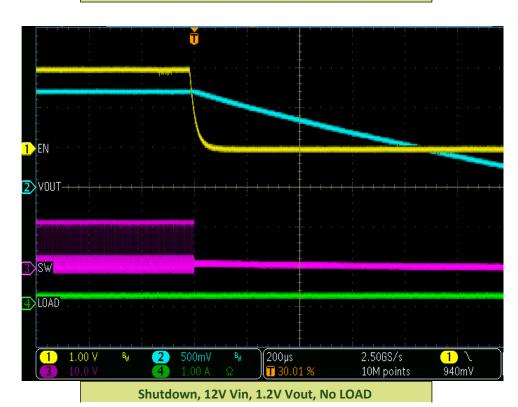

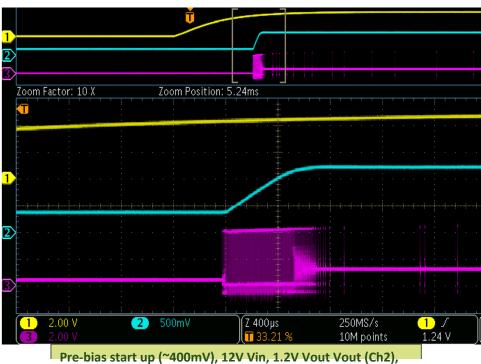

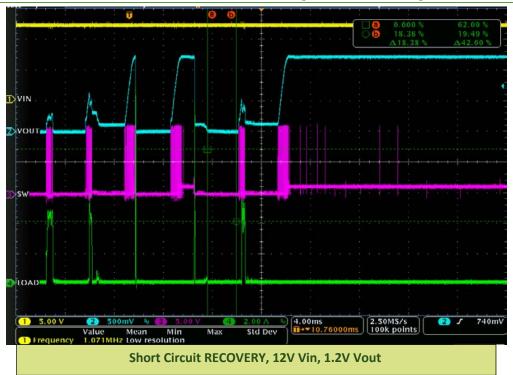

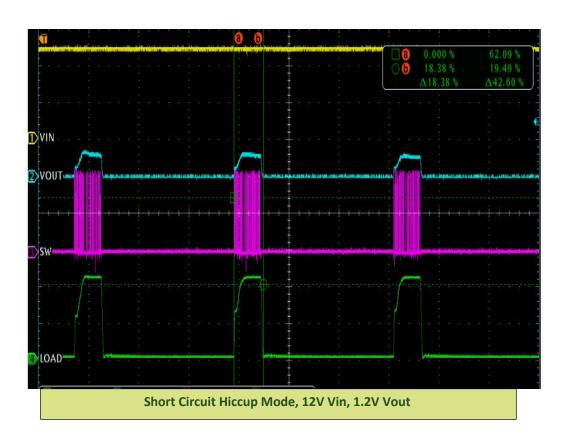

# **Typical Performance Characteristics (Continued)**

# **Typical Performance Characteristics (Continued)**

SW (Ch3), Vin(Ch1)

# **Typical Performance Characteristics (Continued)**

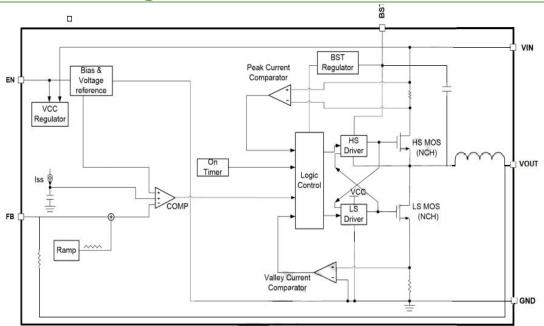

# **Functional Block Diagram**

Figure 3: Functional Block Diagram

## **Functional Description**

The SD11201IQ is a fully integrated, synchronous, rectified, step-down, switch-mode converter. Constant-on-time (COT) control is employed to provide fast transient response and to simplify loop stabilization. At the beginning of each cycle, the high-side MOSFET (HS-FET) is turned on when the FB voltage (VFB) drops below the reference voltage (VREF). The HS-FET is turned on for a fixed interval determined by the one-shot on-timer. The on-timer is determined by both the output voltage and input voltage to make the switching frequency fairly constant over the input voltage range. After the on period elapses, the HS-FET is turned off until the next period begins. By repeating this operation, the converter regulates the output voltage. Continuous conduction mode (CCM) occurs when the output current is high and the inductor current is always above zero amps. The low side MOSFET is turned on when the high side MOSFET is in its off state to minimize conduction loss. To prevent a shoot-through (a short between the input and GND if both the HS-FET and LS-FET are turned on at the same time), a dead time is generated internally between the HS-MOSFET off and LS-MOSFET on, or LS-MOSFET off and HS-MOSFET on.

When the SD11201IQ works in PFM mode during light-load operation, the SD11201IQ reduces the switching frequency automatically to maintain high efficiency, and the inductor current drops almost to zero. When the inductor current reaches zero, the low-side driver enters tri-state (high-Z). The output capacitors discharge slowly to GND through FB divider resistors. When VFB drops below the reference voltage, the HS-FET is turned on. This operation improves device efficiency greatly when the output current is low. During Light-load operation, the HS-FET does not turn on as frequently as it does in heavy-load conditions.

The frequency at which the HS-FET turns on is a function of the output current. As the output current increases, the time period that the current modulator regulates becomes shorter, and the HS-FET turns on more frequently. The switching frequency increases in turn. The output current reaches critical levels when the current modulator time is zero, and can be determined with Equation (1):

# **SD11201IQ Power Module**

High Input Voltage, 1A Buck Converter with Integrated Inductor - 13

$$Iout = \frac{(Vin-Vout) \times Vout}{2 \times L \times Fsw \times Vin}$$

The SD11201IQ reverts to PWM mode once the output current exceeds the critical level. Afterward, the switching frequency remains fairly constant over the output current range.

### **Under-Voltage Lockout (UVLO)**

Under-voltage lock out protection (UVLO) monitors the internal regulator voltage. When the voltage is lower than UVLO threshold voltage, the device is shut down. This protection is non-latching.

### **Enable (EN) Control**

Enable (EN) is a digital control pin that turns the regulator on and off. Drive EN high to turn on the regulator; drive EN low to turn off the regulator. An internal 770 k $\Omega$  resistor from EN to GND allows EN to be floated to shut down the chip. EN is clamped internally using a 3V series Zener diode. EN can be connected to VIN directly to save one pull up resistor.

The SD11201IQ has valley current-limit control. During LS-FET on, the inductor current is monitored. When the sensed inductor current reaches the valley current limit, the LS-MOSFET limit comparator turns over. The device enters over current protection (OCP) mode and the HS-FET waits until the valley current limit disappears before turning on again. The output voltage drops until VFB is below the under voltage (UV) threshold (typically 44% below the reference). Once UV is triggered, the SD11201IQ enters hiccup mode to restart the part periodically. During OCP, the device attempts to recover from the over-current fault with hiccup mode. In hiccup mode, the chip disables the output power stage, discharges the soft start, and attempts to soft start again automatically. If the over-current condition still holds after the soft start ends, the device repeats this operation cycle until the over-current condition is removed and the output rises back to regulation levels. OCP is a non-latch protection.

### Soft Start and Pre-Biased Soft Start

Soft start (SS) prevents the converter output voltage from overshooting and input inrush current during start-up. The SD11201IQ has an internal 0.8ms soft-start. When the EN pin becomes high, the internal soft-start function begins ramping up the reference voltage to the PWM comparator. If the output capacitor is pre-biased at startup, the devices initiate switching and start ramping up only after the internal reference voltage becomes greater than the feedback voltage VFB. This scheme ensures that the converters ramp up smoothly into regulation point.

### Thermal-Shutdown

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. The device monitors the temperature of itself. If the temperature exceeds the threshold value (typically 150°C), the device is shut off. This is a non-latch protection.

### High Input Voltage, 1A Buck Converter with Integrated Inductor - 14

# **Application Information**

### **Output Voltage Setting**

The SD11201IQ output voltage is programmed by setting two resistors, one resistor between FB and VOUT (R<sub>1</sub>) and one resistor between FB and GND (R2). Figure 5 shows the resistor configuration. It is recommended to use  $56k\Omega$  for R1 and adjust R2 to set the output voltage.

**Figure 4: Typical Applications Circuit**

Depending on input and output voltage, the recommended external passive component values are shown in Table 1.

| $V_{IN}$ | V <sub>OUT</sub> | R <sub>1</sub> | R <sub>2</sub> | C <sub>OUT</sub> |

|----------|------------------|----------------|----------------|------------------|

| 12V      | 0.6V             | 56kΩ           | OPEN           |                  |

|          | 1.2V             | 56kΩ           | 56kΩ           |                  |

|          | 1.8V             | 56kΩ           | 28.4kΩ         | 47μF             |

|          | 3.3V             | 56kΩ           | 12.6kΩ         |                  |

|          | 5.0V             | 56kΩ           | 7.68kΩ         |                  |

Table 1: Common external passive component settings

### **Setting other Output Voltages**

To choose output voltage settings other than those stated in table 1, assume R1=  $56k\Omega$ , choose resistor between FB and GND (R<sub>2</sub>), per the formula below:

$$R2 = \frac{33.88}{Vout - 0.605}$$

### High Input Voltage, 1A Buck Converter with Integrated Inductor - 15

### **Input Capacitor Selection**

The input of synchronous buck regulators can be very noisy and should be decoupled properly in order to ensure stable operation. In addition, input parasitic line inductance can attribute to higher input voltage ripple. It is recommended to have a minimum of  $22\mu F$  input capacitance. For improved transient response, use a 100 $\mu F$  input capacitor.

As the distance of the input power source to the input of the SD11201IQ is increased, it is recommended to increase input capacitance in order to mitigate the line inductance from the source. Low-ESR ceramic capacitors should be used. The dielectric must be X5R or X7R rated and the size must be at least 0805 (EIA) due to derating. Y5V or equivalent dielectric formulations must not be used as these lose too much capacitance with frequency, temperature and bias voltage. In some applications, lower value capacitors are needed in parallel with the larger capacitors in order to provide high frequency decoupling. Larger electrolytic or tantalum bulk capacitors may be used in conjunction to increase total input capacitance but should not be used solely as a replacement for the ceramic capacitors.

### **Output Capacitor Selection**

The output ripple of a synchronous buck converter can be attributed to its inductance, switching frequency and output decoupling. It is recommended to have a minimum of  $47\mu\text{F}$  output capacitance. For improved transient response, use one 47uF in parallel with one 100uF capacitor.

Low ESR ceramic capacitors should be used. The dielectric must be X5R or X7R rated and the size must be at least 0805 (EIA) due to derating. Y5V or equivalent dielectric formulations must not be used as these lose too much capacitance with frequency, temperature and bias voltage.

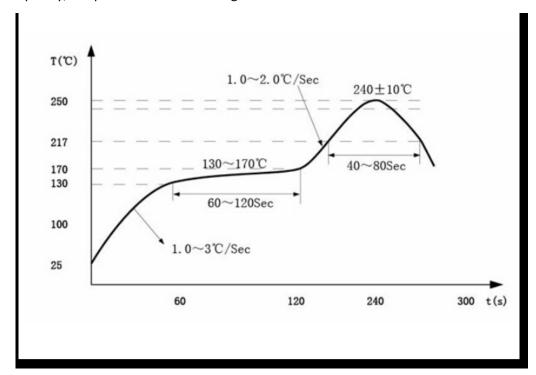

Figure 5: IR Reflow Profile for the 6x4 QFN Package

# **Layout Recommendations**

Devices, Inc.

**Recommendation 1**: Input and output filter capacitors should be placed on the same side of the PCB, and as close to the SD11201IQ package as possible. They should be connected to the device with very short and wide traces. Do not use thermal reliefs or spokes when connecting the capacitor pads to the respective nodes. The Voltage and GND traces between the capacitors and the SD11201IQ should be as close to each other as possible so that the gap between the two nodes is minimized, even under the capacitors.

**Recommendation 2**: Half of the PGND pins are dedicated to the input circuit and the other half to the output circuit. Incorporting a slit separating the input and output GND circuits helps minimize noise coupling between the converter input and output switching loops.

**Recommendation 3**: The system ground plane should be on the 2<sup>nd</sup> layer (below the surface layer). This ground plane should be continuous and un-interrupted.

**Recommendation 4**: The large thermal pad underneath the device must be connected to the system ground plane through as many vias as possible. The drill diameter of the vias should be 0.33mm, and the vias must have at least 1-oz. copper plating on the inside wall, making the finished hole size around 0.2mm to 0.26mm. Do not use thermal reliefs or spokes to connect the vias to the ground plane. This connection provides the path for heat dissipation from the converter.

**Recommendation 5**: Multiple small vias (the same size as the thermal vias discussed in recommendation 4 should be used to connect ground terminal of the input capacitor and output capacitors to the system ground plane. Put the vias under the capacitors along the edge of the GND copper closest to the Voltage copper. These vias connect the input/output filter capacitors to the GND plane, and help reduce parasitic inductance in the input and output current loops. If the vias cannot be placed under  $C_{IN}$  and  $C_{OUT}$ , then put them just outside the capacitors along the GND slit separating the two components. Do not use thermal reliefs or spokes to connect these vias to the ground plane.

**Recommendation 6**: The  $V_{OUT}$  sense point should be connected at the last output filter capacitor furthest from the VOUT pins. Keep the sense trace as short as possible in order to avoid noise coupling into the control loop.

**Recommendation 7**: As with any switch-mode DC-DC converter, try not to run sensitive signal or control lines underneath the converter package on other layers.

Figure 6: Recommended PCB Layout

### High Input Voltage, 1A Buck Converter with Integrated Inductor - 17

## **Package drawings**

Dimensions in mm

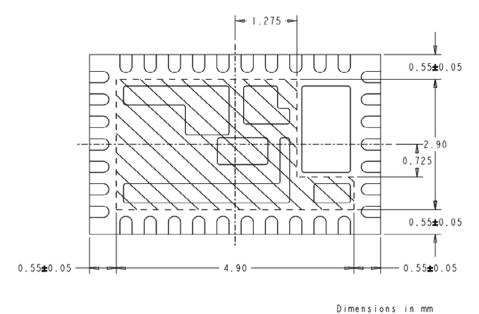

# Design considerations for Lead-frame based modules

### Exposed Metal on Bottom of Package

Only the thermal pad and the perimeter pads are to be mechanically or electrically connected to the board. The PCB top layer under the SD11201IQ should be clear of any metal (copper pours, traces, or vias) except for the thermal pad. The "shaded-out" area in Figure 9 represents the area that should be clear of any metal on the top layer of the PCB. Any layer 1 metal under the shaded-out area runs the risk of undesirable shorted connections even if it is covered by solder mask.

The solder stencil aperture should be smaller than the PCB ground pad. This will prevent excess solder from causing bridging between adjacent pins or other exposed metal under the package.

Figure 7: Lead-Frame exposed metal (Bottom View)

Shaded area highlights exposed metal that is not to be mechanically or electrically connected to the PCB.

© 2021 Solitron Devices, Inc.

This document is believed to be correct at the time of publication and Solitron Devices accepts no responsibility for consequences from printing errors or inaccuracies. All specifications are subject to change without notice.